ETR0212-004a

### Voltage Detector with Delay Circuit Built-In

#### **■**GENERAL DESCRIPTION

The XC61H series is a highly accurate, low power consumption CMOS voltage detector with a delay circuit. Detect voltage is accurate with minimal temperature drift. Output configurations are available in both CMOS and N-channel open drain. Since the full delay circuit is built-in, an external delay-time capacitor is not necessary so that high density mounting is possible.

#### APPLICATIONS

- Microprocessor reset circuitry

- System battery life and charge voltage monitors

- Memory battery back-up circuits

- Power-on reset circuits

- Power failure detection

- Delay circuitry

#### **■**FEATURES

**Detect Voltage Accuracy** : ± 2%

**Low Power Consumption** :  $1.0 \,\mu$  A(TYP.)[  $V_{IN}=2.0V$  ] **Detect Voltage Range** : 1.6V ~ 6.0V (0.1V increments)

**Operating Voltage Range** : 0.7V ~ 10.0V **Detect Voltage Temperature Characteristics**

: ±100ppm/°C(TYP.)

Built-In Release Delay time: 1ms (MIN.)

50ms (MIN.) 80ms (MIN.)

**Output Configuration** : N-ch open drain output or CMOS

Operating Ambient Temperature : -30°C~80°C **Package** : SOT-23

Environmentally Friendly : EU RoHS Compliant, Pb Free

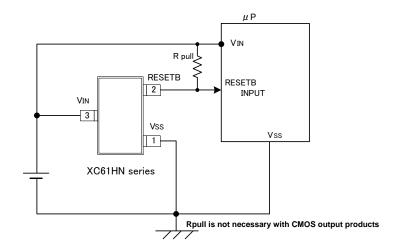

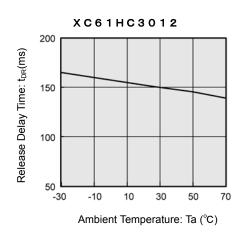

## ■TYPICAL APPLICATION CIRCUITS ■TYPICAL PERFORMANCE

# CHARACTERISTICS

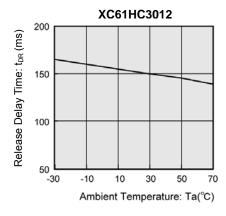

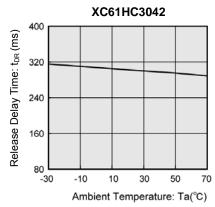

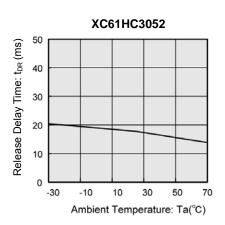

● Release Delay Time (t<sub>DR</sub>) vs. Ambient Temperature

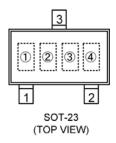

#### **■ PIN CONFIGURATION**

#### **■PIN ASSIGNMENT**

| PIN NUMBER | PIN NAME        | FUNCTION             |  |

|------------|-----------------|----------------------|--|

| SOT-23     | PIN NAIVIE      | FUNCTION             |  |

| 1          | Vss             | Ground               |  |

| 2          | RESETB          | Output               |  |

| 3          | V <sub>IN</sub> | Supply Voltage Input |  |

### **■PRODUCT CLASSIFICATION**

Ordering Information

#### XC61H1234567-8(\*1)

| DESIGNATOR                | ITEM                   | SYMBOL  | DESCRIPTION            |  |

|---------------------------|------------------------|---------|------------------------|--|

| <u> </u>                  | Output Configuration   | С       | CMOS output            |  |

| 1                         | Output Configuration   | N       | N-ch open drain output |  |

| 23                        | Detect Voltage (VDF)   | 16 ~ 60 | e.g. 2.5V → ②2, ③5     |  |

|                           |                        | 1       | 50ms ~ 200ms           |  |

| 4                         | Release Delay Time     | 4       | 80ms ~ 400ms           |  |

|                           |                        | 5       | 1ms ~ 50ms             |  |

| 5                         | Detect Accuracy        | 2       | ± 2.0% <sup>(*2)</sup> |  |

| <b>6</b> 7- <b>8</b> (*1) | Package<br>(Oder Unit) | MR-G    | SOT-23 (3000pcs/Reel)  |  |

<sup>(\*1)</sup> The "-G" suffix indicates that the products are Halogen and Antimony free as well as being fully RoHS compliant.

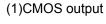

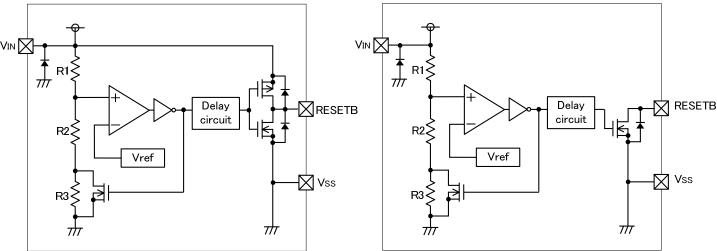

### **■BLOCK DIAGRAMS**

#### (2)N-ch open drain output

<sup>(\*2)</sup> No parts are available with an accuracy of  $\pm$  1%

## ■ ABSOLUTE MAXIMUM RATINGS

Ta=25°C

| PARAMETER                     |                        | SYMBOL              | RATINGS                                    | UNITS |  |

|-------------------------------|------------------------|---------------------|--------------------------------------------|-------|--|

| Input Voltage                 |                        | $V_{IN}$            | V <sub>SS</sub> -0.3 ~ 12.0                | V     |  |

| Output Current                |                        | Іоит                | 50                                         | mA    |  |

| Output Voltage                | CMOS                   | \/                  | V <sub>SS</sub> -0.3 ~V <sub>IN</sub> +0.3 | V     |  |

|                               | N-ch open drain output | V <sub>RESETB</sub> | V <sub>SS</sub> -0.3 ~ 12                  |       |  |

| Power Dissipation SOT-23      |                        | Pd                  | 250                                        | mW    |  |

| Operating Ambient Temperature |                        | Topr                | -30~+80                                    | လူ    |  |

| Storage Temperature           |                        | Tstg                | -40~+125                                   | °C    |  |

### **■**ELECTRICAL CHARACTERISTICS

Ta = 25°C

| PARA                       | AMETER                                                                                                                    | SYMBOL            | CONDITIO                                                         | ONS                    | MIN.                         | TYP.                   | MAX.                      | UNITS | CIRCUIT |  |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------|------------------------|------------------------------|------------------------|---------------------------|-------|---------|--|

| Detec                      | ct Voltage                                                                                                                | $V_{DF}$          |                                                                  |                        | V <sub>DF(T)</sub><br>x 0.98 | $V_{DF(T)}$            | V <sub>DF(T)</sub> x 1.02 | V     | 1       |  |

| Hyster                     | esis Width                                                                                                                | V <sub>H</sub> YS |                                                                  |                        | V <sub>DF</sub> x 0.02       | V <sub>DF</sub> x 0.05 | V <sub>DF</sub> x 0.08    | V     | 1       |  |

|                            |                                                                                                                           |                   |                                                                  | V <sub>IN</sub> = 1.5V | -                            | 0.9                    | 2.6                       |       |         |  |

|                            |                                                                                                                           |                   | V <sub>IN</sub> = 2.0                                            |                        | ı                            | 1.0                    | 3.0                       |       |         |  |

| Supply                     | Current (*1)                                                                                                              | Iss               |                                                                  | V <sub>IN</sub> = 3.0V | -                            | 1.3                    | 3.4                       | μΑ    | 2       |  |

|                            |                                                                                                                           |                   |                                                                  | $V_{IN} = 4.0V$        | -                            | 1.6                    | 3.8                       |       |         |  |

|                            |                                                                                                                           |                   |                                                                  | $V_{IN} = 5.0V$        | -                            | 2.0                    | 4.2                       |       |         |  |

| Operati                    | ing Voltage                                                                                                               | $V_{IN}$          | V <sub>DF</sub> =1.6V∼6.0V                                       |                        | 0.7                          | -                      | 10.0                      | V     | 1       |  |

|                            |                                                                                                                           |                   |                                                                  | V <sub>IN</sub> = 1.0V | 1.0                          | 2.2                    | -                         | mA    | 3       |  |

|                            |                                                                                                                           |                   | N-ch, V <sub>DS</sub> = 0.5V                                     | $V_{IN} = 2.0V$        | 3.0                          | 7.7                    | -                         |       |         |  |

|                            |                                                                                                                           | Іоит              |                                                                  | $V_{IN} = 3.0V$        | 5.0                          | 10.1                   | -                         |       |         |  |

| Outpu                      | ut Current                                                                                                                |                   |                                                                  | V <sub>IN</sub> = 4.0V | 6.0                          | 11.5                   | -                         |       |         |  |

|                            |                                                                                                                           |                   |                                                                  | $V_{IN} = 5.0V$        | 7.0                          | 13.0                   | -                         |       |         |  |

|                            |                                                                                                                           |                   | P-ch, V <sub>DS</sub> =2.1V<br>(CMOS Output)                     | V <sub>IN</sub> = 8.0V |                              | -10.0                  | -2.0                      |       | 4       |  |

| Leakage                    | CMOS Output<br>(Pch)                                                                                                      | I <sub>LEAK</sub> | V <sub>IN</sub> =V <sub>DF</sub> x 0.9V, V <sub>RESETB</sub> =0V |                        | -                            | -0.01                  | -                         | μΑ    | 3       |  |

| Current                    | Nch Open<br>Drain Output                                                                                                  |                   | V <sub>IN</sub> =10.0V, V <sub>RESETB</sub> =10.0V               |                        | -                            | 0.01                   | 0.1                       |       |         |  |

|                            | ct Voltage $\Delta V_{DF}/$ e Characteristics $\Delta V_{DF}/$ $\Delta V_{DF}/$ $-30^{\circ}C \leq Topr \leq 80^{\circ}C$ |                   | -                                                                | ±100                   | -                            | ppm/°C                 | 1                         |       |         |  |

| Release                    | Release Delay Time                                                                                                        |                   | t <sub>DR</sub> VIN changes from 0.6V to 10V                     |                        | 50                           | -                      | 200                       | ms    | 5       |  |

|                            | (VDR → RESETB inversion)                                                                                                  |                   |                                                                  |                        | 80                           | -                      | 400                       |       |         |  |

| (VDR - RESETB IIIVEISIOII) |                                                                                                                           |                   |                                                                  |                        | 1                            | -                      | 50                        |       |         |  |

VDF (T) is nominal detect voltage value Release Voltage: VDR = VDF + VHYS

<sup>(\*1)</sup> The supply current during power-start until output being stable (during release operation) is 2  $\mu$  A greater with comparison to the period after the completion of release operation because of the shoot-through current in delay current.

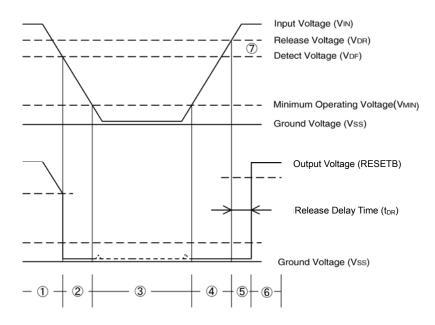

#### ■ OPERATIONAL EXPLANATION

#### CMOS output

- (1) An input voltage V<sub>IN</sub> starts higher than the release voltage V<sub>DR</sub>. Then, V<sub>IN</sub> voltage will gradually fall. When V<sub>IN</sub> voltage is higher than detect voltage V<sub>DF</sub>, output voltage RESETB is equal to the V<sub>IN</sub> voltage.

- \*Note that high impedance exists at RESETB with the N-channel open drain output configuration. If the RESETB pin is pulled up, RESETB will be equal to the pull up voltage.

- ② When VIN falls below VDF, RESETB will be equal to ground voltage Vss level (detect state).

- \* Note that this also applies to N-channel open drain output configurations.

- When VIN falls to a level below that of the minimum operating voltage VMIN, output will become unstable.

\*When the output pin is generally pulled up with N-channel open drain output configurations, output will be equal to pull up voltage.

- When Vin rises above the Vss level (excepting levels lower than minimum operating voltage), RESETB will be equal to Vss until Vin reaches the VDR level.

- S Although Vin will rise to a level higher than VDR, RESETB maintains ground voltage level via the delay circuit.

- After taking a release delay time, VIN voltage will be output at the RESETB pin.

\*High impedance exists with the N-channel open drain output configuration and that voltage will be dependent on pull up.

#### Notes:

- 1. The difference between VDR and VDF represents the hysteresis width.

- 2. Release delay time (t<sub>DR</sub>) represents the time it takes until when V<sub>IN</sub> voltage appears at RESETB pin once the input voltage has exceeded the V<sub>DR</sub> level.

#### Timing Chart

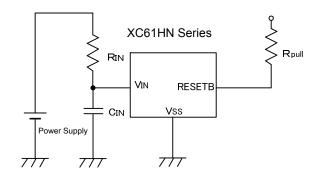

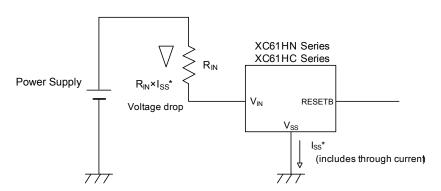

#### ■NOTES ON USE

- 1. Please use this IC within the stated maximum ratings. For temporary, transitional voltage drop or voltage rising phenomenon, the IC is liable to malfunction should the ratings be exceeded.

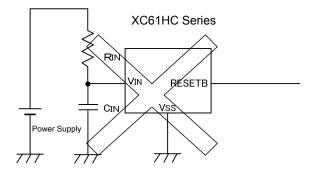

- 2. When a resistor is connected between the V<sub>IN</sub> pin and the power supply with CMOS output configurations, irregular oscillation may occur as a result of voltage drops at R<sub>IN</sub> if load current (I<sub>OUT</sub>) exists. It is therefore recommend that no resistor be added. (refer to Figure 1 below)

- 3. When a resistor (R<sub>IN</sub>) is connected between the V<sub>IN</sub> pin and the power supply with CMOS output configurations, irrespective of N-ch open drain output configurations, oscillation may occur as a result of shoot-through current at the time of voltage release even if load current (I<sub>OUT</sub>) does not exist. (refer to Figure 2 below)

- 4. If a resistor (R<sub>IN</sub>) must be used, then please use with as small a level of input impedance as possible in order to control the occurrences of oscillation as described above. Further, please ensure that R<sub>IN</sub> is less than 10kΩ and that C<sub>IN</sub> is more than 0.1 μF, please test with the actual device. However, N-ch open drain output only. (Figure 1).

- 5. With a resistor RIN connected between the VIN pin and the power supply, the VIN pin voltage will be getting lower than the power supply voltage as a result of the IC's supply current flowing through the VIN pin.

- 6. Depending on circuit's operation, release delay time of this IC can be widely changed due to upper limits or lower limits of operational ambient temperature.

- 7. Torex places an importance on improving our products and its reliability.

However, by any possibility, we would request user fail-safe design and post-aging treatment on system or equipment.

#### Irregular Oscillations

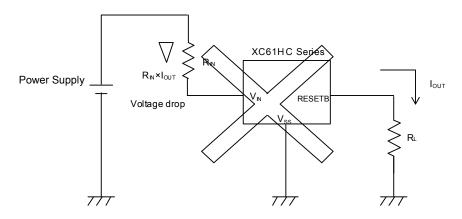

(1) Irregular oscillation as a result of load current with the CMOS output configuration:

When the voltage applied at power supply, release operations commence and the detector's output voltage increases. Load current ( $I_{OUT}$ ) will flow through  $R_L$ . Because a voltage drop ( $R_{IN} \times I_{OUT}$ ) is produced at the  $R_{IN}$  resistor, located between the power supply and the  $V_{IN}$  pin, the load current will flow via the IC's  $V_{IN}$  pin. The voltage drop will also lead to a fall in the voltage level at the  $V_{IN}$  pin. When the  $V_{IN}$  pin voltage level falls below the detect voltage level, detect operations will commence. Following detect operations, load current flow will cease and since voltage drop at  $R_{IN}$  will disappear, the voltage level at the  $V_{IN}$  pin will rise and release operations will begin over again. Irregular oscillation may occur with this "release - detect - release" repetition.

Further, this condition will also appear via means of a similar mechanism during detect operations.

(2) Irregular oscillation as a result of shoot-through current:

Since the XC61H series are CMOS ICs, shoot-through current will flow when the IC's internal circuit switching operates (during release and detect operations). Consequently, irregular oscillation is liable to occur during release voltage operations as a result of output current which is influenced by this shoot-through current (Figure 3). Since hysteresis exists during detect operations, irregular oscillation is unlikely to occur.

Figure 1 Use of input resistor RIN

## ■NOTES ON USE (Continued)

Irregular Oscillations (Continued)

#### XC61HC Series

Figure 2 Irregular Oscillation by output current

## XC61HC Series XC61HN Series

Figure 3 Irregular Oscillation by shoot-through current

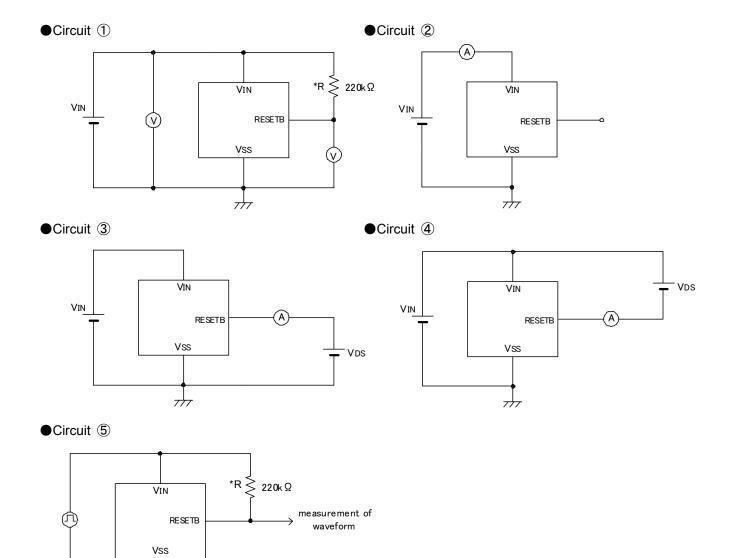

## **■**TEST CIRCUITS

\*R is not necessary with CMOS output products.

#### **■**TYPICAL PERFORMANCE CHARACTERISTICS

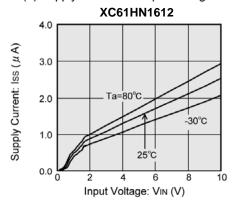

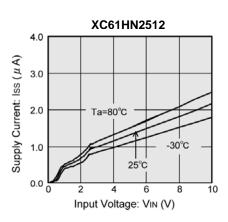

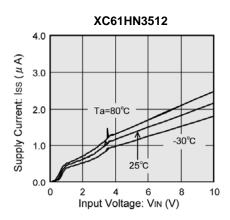

(1) Supply Current vs. Input Voltage

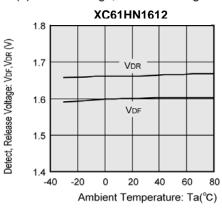

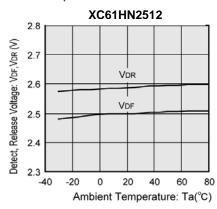

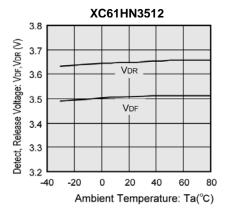

(2) Detect Voltage, Release Voltage vs. Ambient Temperature

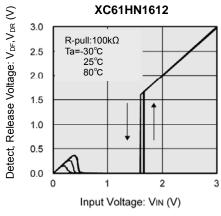

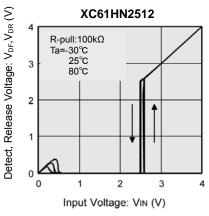

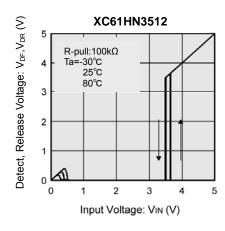

(3) Detect Voltage, Release Voltage vs. Input Voltage

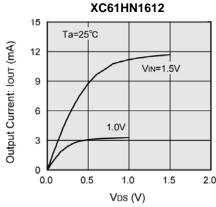

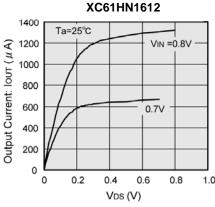

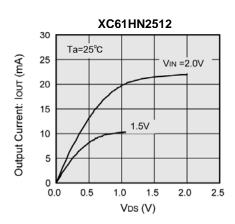

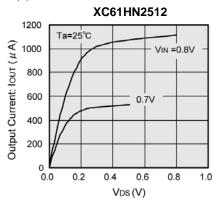

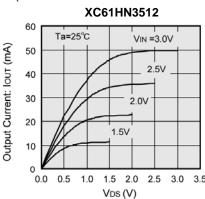

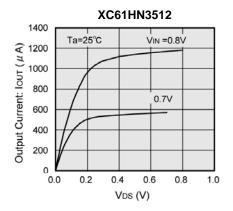

(4) N-Channel Driver Output Current vs. VDS

## ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

(4) N-Channel Driver Output Current vs. VDS (Continued)

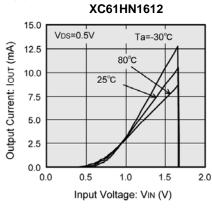

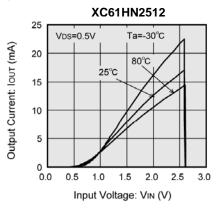

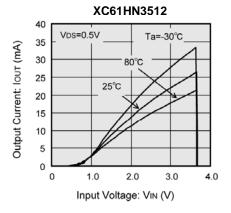

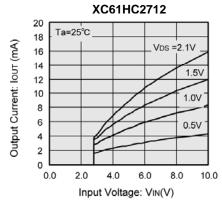

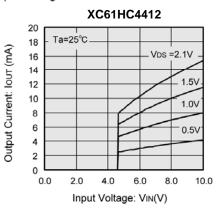

(5) N-Channel Driver Output Current vs. Input Voltage

(6) P-Channel Driver Output Current vs. Input Voltage

(7) Ambient Temperature vs. Release Delay Time (t<sub>DR</sub>)

## ■TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

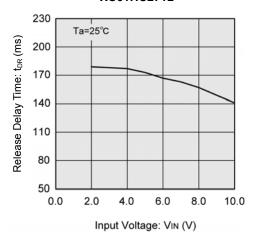

(8) Input Voltage vs. Release Delay Time  $(t_{DR})$

#### XC61HC2712

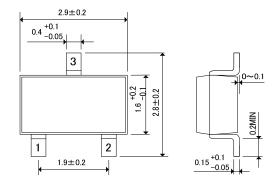

## ■ PACKAGING INFORMATION

#### ●SOT-23

(unit:mm)

## XC61H Series

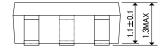

### **■**MARKING RULE

#### ●SOT-23

① represents product series

| MARK | PRODUCTS SERIES |

|------|-----------------|

| 8    | XC61H******-G   |

2 standard : represents output configuration and integer number of detect voltage

CMOS output (XC61HC series)

| MARK | VOLTAGE<br>(V) |  |  |

|------|----------------|--|--|

| Α    | 1. X           |  |  |

| В    | 2. X           |  |  |

| С    | 3. X           |  |  |

| D    | 4. X           |  |  |

| E    | 5. X           |  |  |

| F    | 6. X           |  |  |

N-channel open drain (XC61HN series)

| MARK | VOLTAGE<br>(V) |  |

|------|----------------|--|

| Р    | 1. X           |  |

| R    | 2. X           |  |

| S    | 3. X           |  |

| Т    | 4. X           |  |

| U    | 5. X           |  |

| V    | 6. X           |  |

③ represents decimal number of detect voltage and delay time.

| DETECT         | MARK                                         |                                              |                                            |  |  |  |

|----------------|----------------------------------------------|----------------------------------------------|--------------------------------------------|--|--|--|

| VOLTAGE<br>(V) | DELAY TIME<br>50ms~200ms<br>(XC61H***1***-G) | DELAY TIME<br>80ms~400ms<br>(XC61H***4***-G) | DELAY TIME<br>1ms~50ms<br>(XC61H***5***-G) |  |  |  |

| X.0            | 0                                            | A                                            | N                                          |  |  |  |

| X.1            | 1                                            | В                                            | Р                                          |  |  |  |

| X.2            | 2                                            | С                                            | R                                          |  |  |  |

| X.3            | 3                                            | D                                            | S                                          |  |  |  |

| X.4            | 4                                            | E                                            | Т                                          |  |  |  |

| X.5            | 5                                            | F                                            | U                                          |  |  |  |

| X.6            | 6                                            | Н                                            | V                                          |  |  |  |

| X.7            | 7                                            | K                                            | X                                          |  |  |  |

| X.8            | 8                                            | L                                            | Y                                          |  |  |  |

| X.9            | 9                                            | M                                            | Z                                          |  |  |  |

<sup>4</sup> represents production lot number

0 to 9, A to Z or inverted characters of 0 to 9, A to Z repeated.

(G, I, J, O, Q,W excluded)

\*No character inversion used.

- 1. The product and product specifications contained herein are subject to change without notice to improve performance characteristics. Consult us, or our representatives before use, to confirm that the information in this datasheet is up to date.

- 2. The information in this datasheet is intended to illustrate the operation and characteristics of our products. We neither make warranties or representations with respect to the accuracy or completeness of the information contained in this datasheet nor grant any license to any intellectual property rights of ours or any third party concerning with the information in this datasheet.

- Applicable export control laws and regulations should be complied and the procedures required by such laws and regulations should also be followed, when the product or any information contained in this datasheet is exported.

- 4. The product is neither intended nor warranted for use in equipment of systems which require extremely high levels of quality and/or reliability and/or a malfunction or failure which may cause loss of human life, bodily injury, serious property damage including but not limited to devices or equipment used in 1) nuclear facilities, 2) aerospace industry, 3) medical facilities, 4) automobile industry and other transportation industry and 5) safety devices and safety equipment to control combustions and explosions. Do not use the product for the above use unless agreed by us in writing in advance.

- 5. Although we make continuous efforts to improve the quality and reliability of our products; nevertheless Semiconductors are likely to fail with a certain probability. So in order to prevent personal injury and/or property damage resulting from such failure, customers are required to incorporate adequate safety measures in their designs, such as system fail safes, redundancy and fire prevention features.

- 6. Our products are not designed to be Radiation-resistant.

- 7. Please use the product listed in this datasheet within the specified ranges.

- 8. We assume no responsibility for damage or loss due to abnormal use.

- 9. All rights reserved. No part of this datasheet may be copied or reproduced unless agreed by Torex Semiconductor Ltd in writing in advance.

TOREX SEMICONDUCTOR LTD.